Beschreibung

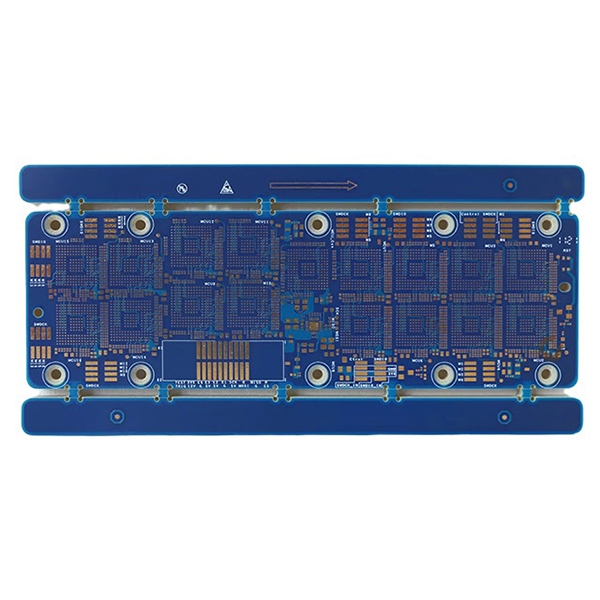

14-lagige, 3-stufige Leiterplattenfertigung für Halbleitertestplatinen

Die Herstellung von 14-lagigen, 3-stufigen Halbleiter-Testplatinen-Leiterplatten mit ihrer hohen Dichte, hohen Präzision und hohen Zuverlässigkeit wird häufig in verschiedenen fortschrittlichen Halbleiter-Testgeräten eingesetzt und dient als wichtige Grundlage für die Sicherstellung der Chip-Qualität und -Leistung.

Hauptmerkmale der Herstellung von 14-lagigen, 3-stufigen Halbleiter-Testplatinen

- Mehrschichtige hochdichte Verbindung:Die 14-lagige Struktur in Kombination mit der 3-stufigen HDI-Technologie unterstützt komplexe Schaltungslayouts und die Isolierung mehrerer Signale und erfüllt damit die Anforderungen an eine hochdichte und schnelle Signalübertragung.

- Präzisionsfertigungsprozess:Verwendet hochwertiges Shengyi S1000-2M-Material mit vergoldeter Oberfläche, einem Mindestlochdurchmesser von 0,5 mm und einem Mindestabstand von 4/4 mil, geeignet für Feinraster- und Hochpräzisionstests.

- Hohe Zuverlässigkeit und Signalintegrität:Fortschrittliche Buried/Blind-Via-Technologie und Zwischenlagenverbindungen verbessern die Signalintegrität und die Störfestigkeit erheblich und gewährleisten genaue Testdaten.

- Hervorragende Materialien und Verarbeitung:Hohe Temperatur- und Korrosionsbeständigkeit, geeignet für langfristige und komplexe Testumgebungen.

- Flexibles Design und Anpassungsmöglichkeiten:Unterstützt verschiedene Testschnittstellen und kundenspezifische Designs, wodurch die Integration in verschiedene Testsysteme vereinfacht wird.

Einführung in die 14-lagige, 3-stufige Halbleiter-Testplatine

- 14 Schichten:Bezieht sich auf 14 leitfähige Schichten innerhalb der Leiterplatte, die komplexe Schaltungsverbindungen und Signalisolierung durch mehrschichtige Stapelung ermöglichen, für Anforderungen an hohe Dichte und hohe Geschwindigkeit geeignet sind und die Signalintegrität und elektromagnetische Verträglichkeit fördern.

- 3 Schritte:Bezieht sich in der Regel auf die „Schritte” in der HDI-Technologie (High Density Interconnect) – drei Laserbohr- und drei Laminierungsprozesse, die feinere vergrabene/blinde Durchgangsstrukturen für flexiblere Verbindungen und eine höhere Dichte unterstützen und für Hochgeschwindigkeits-/Hochfrequenzanwendungen geeignet sind.

- Halbleiter-Testplatine:Speziell für Funktionen wie Chip-Funktionstests und Alterungstests verwendet, die eine hohe Zuverlässigkeit, hohe Präzision und ausgezeichnete Signalübertragungsfähigkeit erfordern.

Hauptanwendungen

- Halbleiter-Testsysteme wie Chip-Test-Handler, automatische Testgeräte (ATE), Prüfkarten und Lastplatinen.

- Anspruchsvolle Testszenarien wie IC-Funktionstests, Alterungstests und Fehleranalysen.

- Geeignet für Halbleiterverpackung und -prüfung sowie für Forschungs- und Entwicklungsbereiche mit Anforderungen an hohe Frequenz, hohe Geschwindigkeit, hohe Präzision und hohe Zuverlässigkeit.

English

English  Français

Français  Tiếng Việt

Tiếng Việt  Italiano

Italiano  Nederlands

Nederlands  Türkçe

Türkçe  Svenska

Svenska  Polski

Polski  Română

Română  Latviešu

Latviešu  한국어

한국어  Русский

Русский  Español

Español  Deutsch

Deutsch  Українська

Українська  Português

Português  العربية

العربية  Indonesian

Indonesian  Čeština

Čeština  Suomi

Suomi  Eesti

Eesti  Български

Български  Dansk

Dansk  Lietuvių

Lietuvių  Bokmål

Bokmål  Slovenčina

Slovenčina  Slovenščina

Slovenščina  Ελληνικά

Ελληνικά  Magyar

Magyar  עברית

עברית